- 应用

- ESD 测试

静电放电测试和模拟

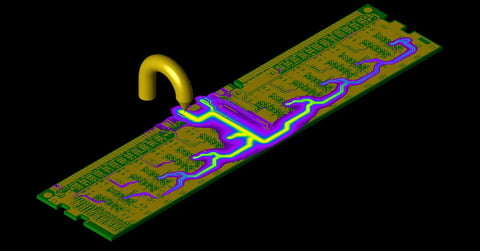

全世界的电子产品制造商都在使用静电放电测试来确定其设备的静电放电敏感性。要估算每年 ESD 损失的确切成本极其困难,但可以肯定的是,ESD 需要开发和测试许多硬件原型,如果在客户手中出现故障,则会导致大量保修索赔和消费者信心损失。

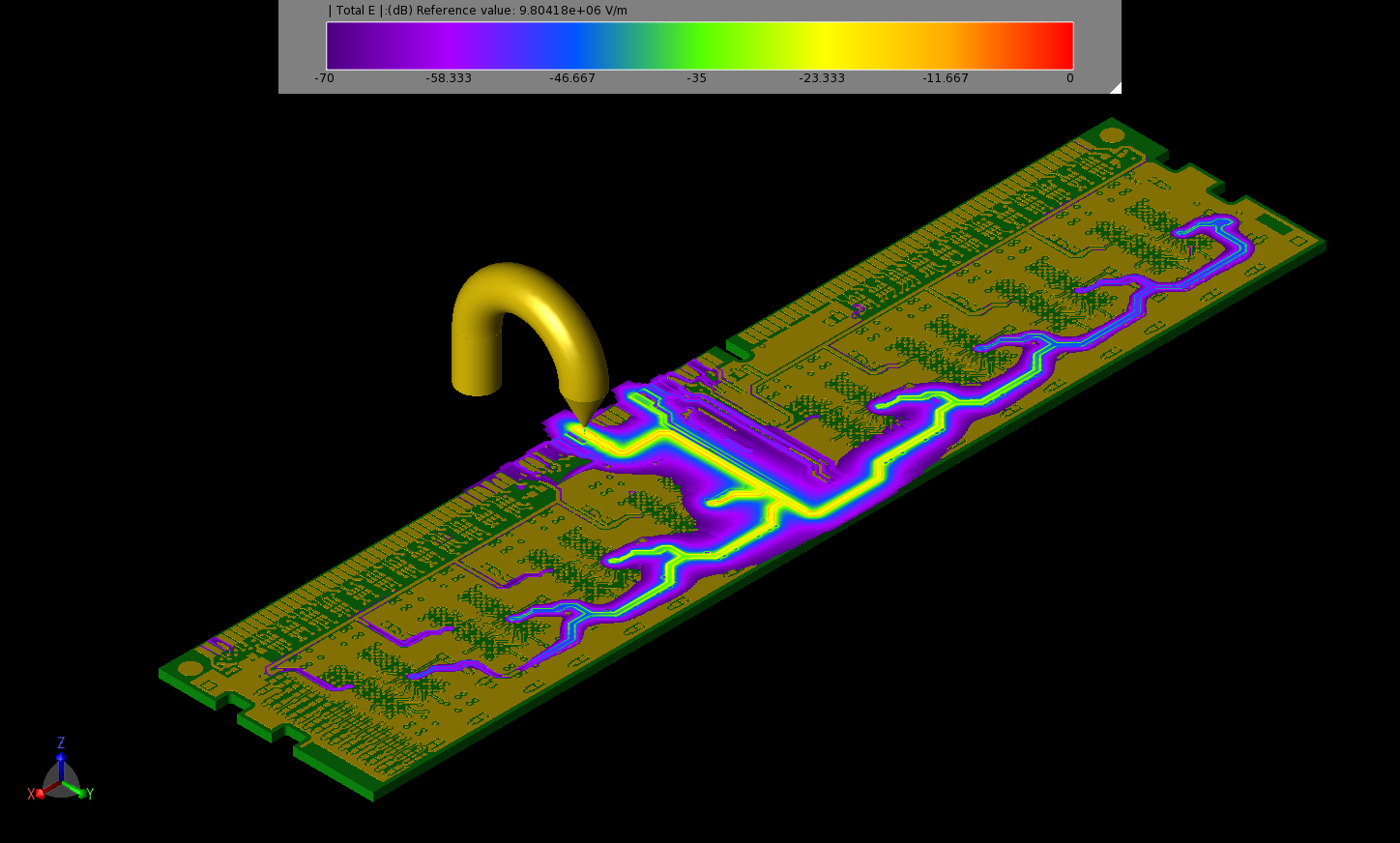

考虑到与 ESD 硬件测试相关的高昂时间和材料成本,在 XFdtd 中模拟 ESD 测试过程的能力极具价值。利用 XFdtd 的静电放电测试模拟功能,工程师可以在产品开发的概念和设计阶段准确定位易受 ESD 损坏的位置,并优化 ESD 缓解措施。

XFdtd 3D EM 仿真软件中的 ESD 测试仿真

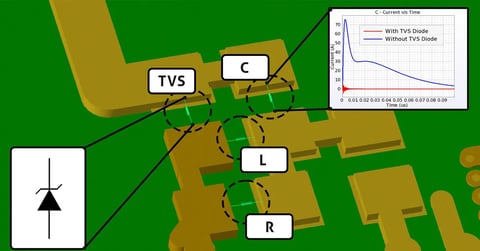

TVS 二极管

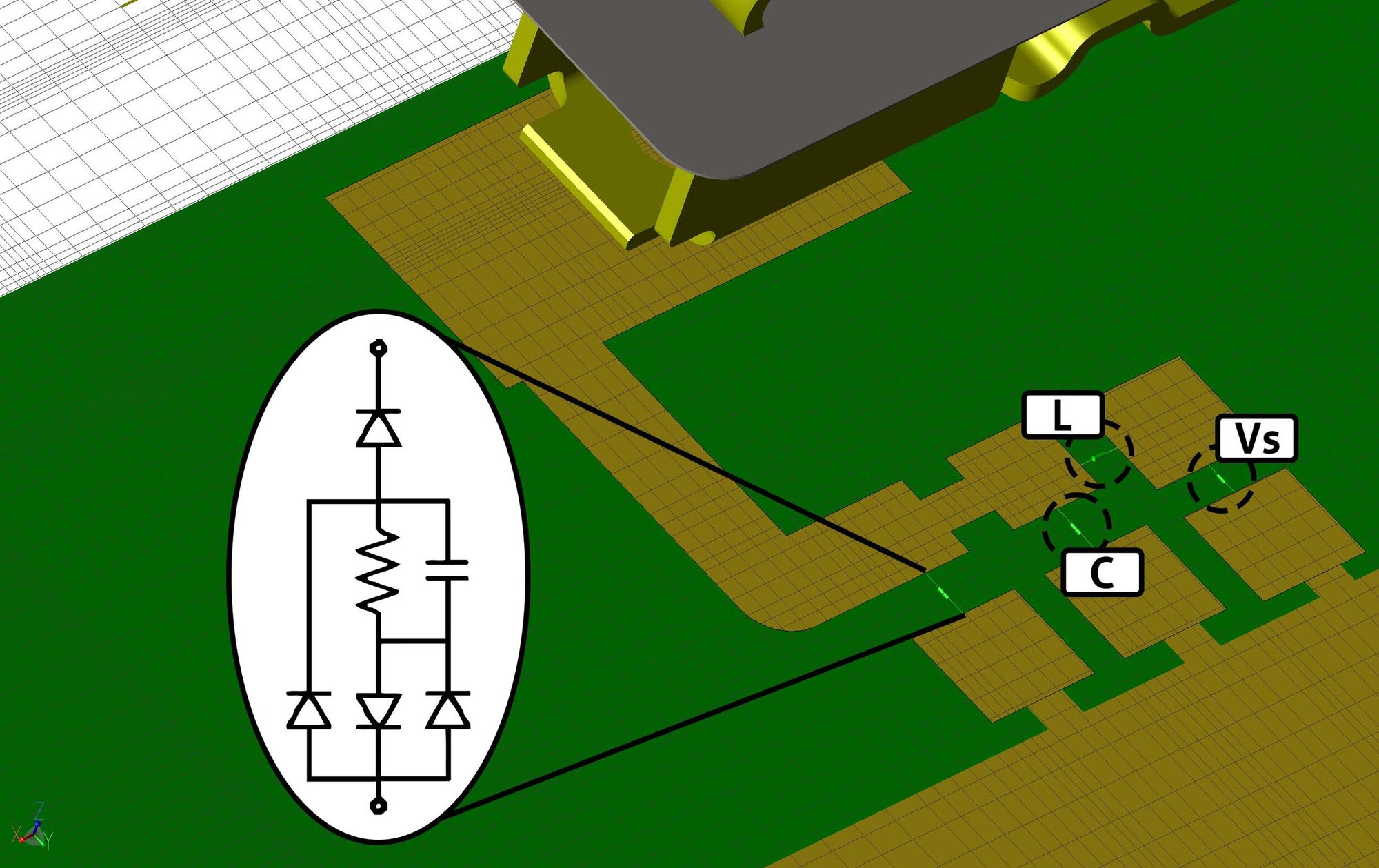

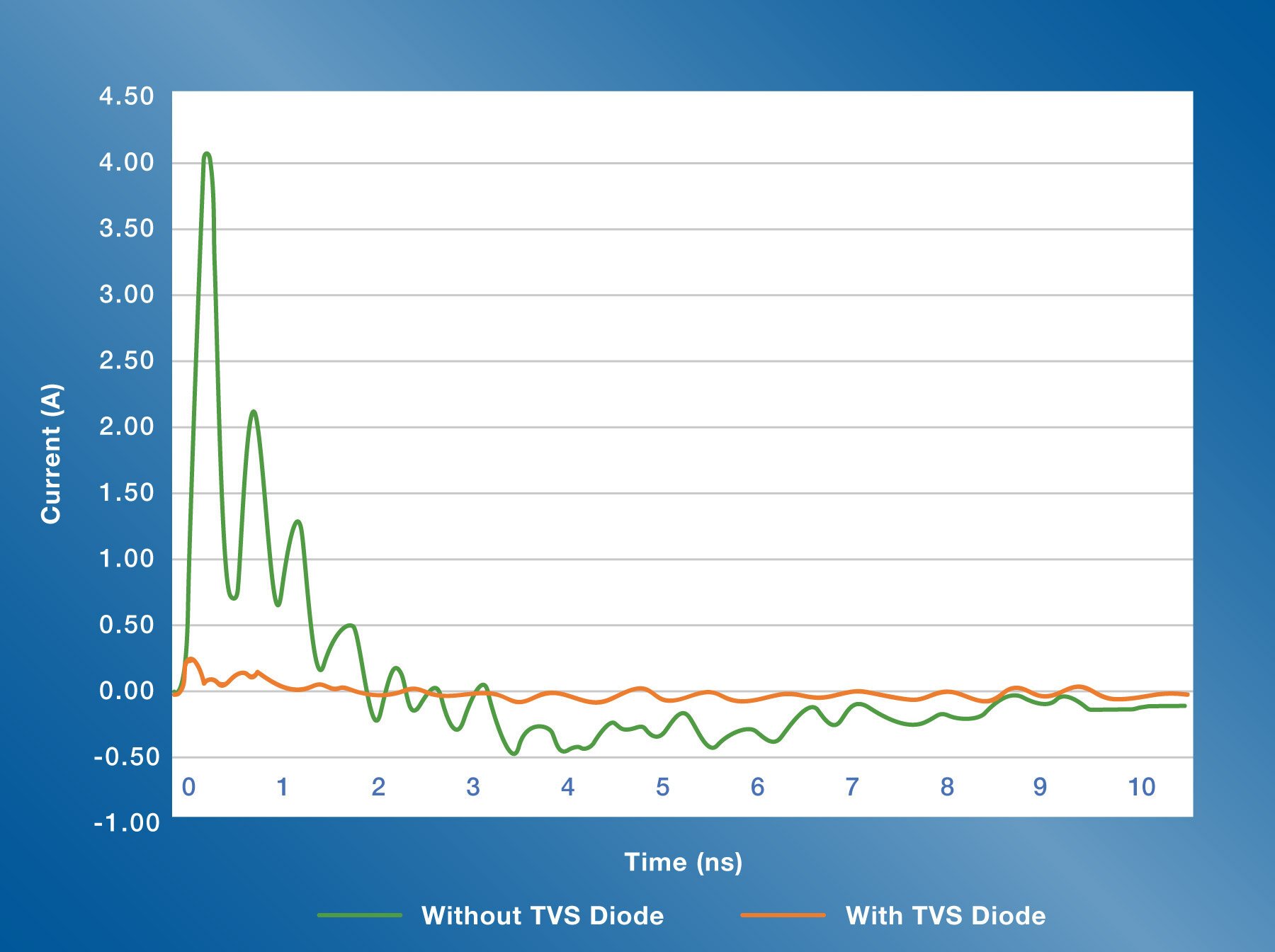

集成电路在设备的射频前端(RFFE)中越来越普遍。在支持更多功能的同时,它们的尺寸也在缩小。其结果是对 ESD 事件和劣化的敏感性增加。TVS 二极管和其他非线性 ESD 缓解元件可保护敏感电路,并在强 ESD 信号到达 RFFE 之前将其重定向到地。XFdtd 的瞬态电磁/电路协同仿真功能可在全波环境中对这些器件进行仿真,并在全波环境中进行系统级分析。

介质击穿预测

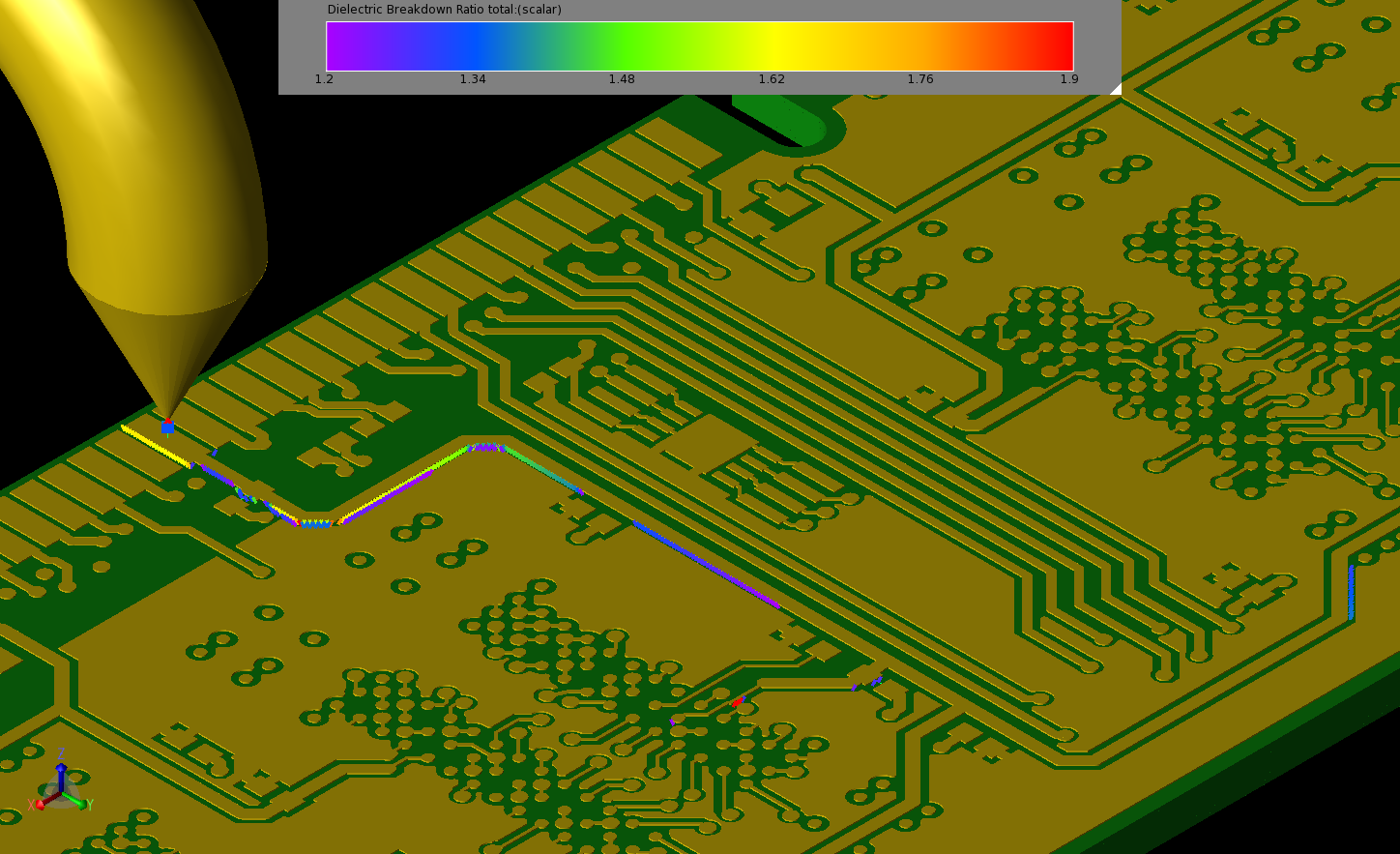

即使是经验丰富的工程师,要在测试过程中精确定位 ESD 失效的位置,甚至在某些情况下确定是否发生了失效,也是极具挑战性的。为了解决这个问题,可以在 XFdtd 中定义材料的介电强度。材料的介电强度定义了材料在不发生介电击穿(即失去绝缘性能)的情况下所能承受的最大电场。在 XFdtd 项目中添加材料的介电强度后,就可以使用介电击穿近场传感器在瞬态模拟过程中监测 FDTD 单元边缘是否存在潜在的介电击穿。在 XFdtd 模拟结束时,可以轻松找到超出介电强度的单元边缘。

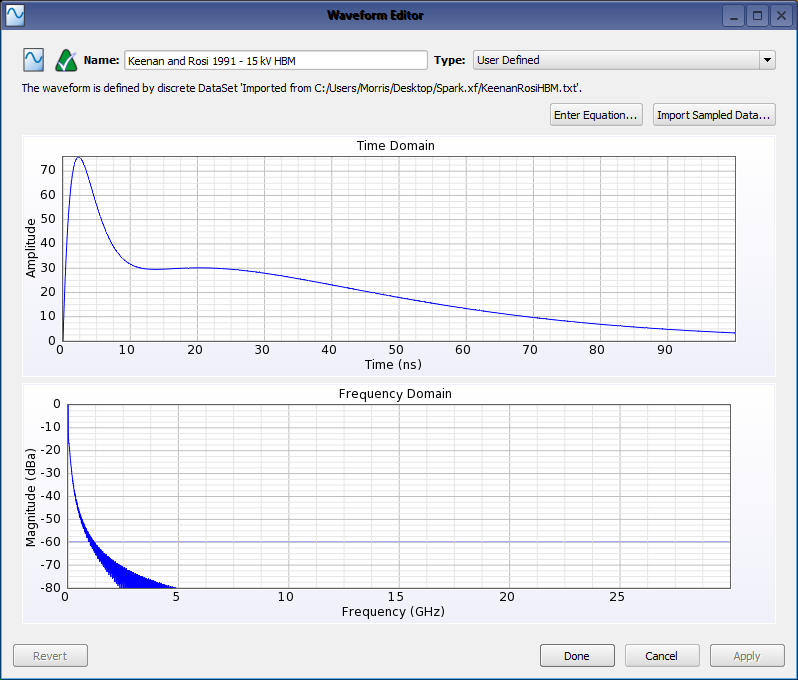

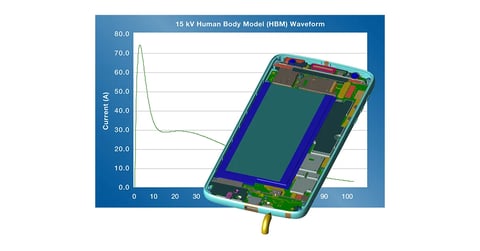

静电放电波形

美国国家标准协会 (ANSI)、JEDEC 和国际电工委员会 (IEC) 等组织的众多标准规定了 ESD 测试程序和波形模型。 人体模型 (HBM) 和带电设备模型 (CDM) 是最常见和广泛使用的 ESD 模型,前者近似于带电人体指尖对接地设备的放电,后者近似于带电设备对静电电位较低的另一导电物体的放电。 这些测试通常使用 ESD 模拟器或 ESD Guns 进行,对被测设备 (DUT) 的各个点施加高速高压脉冲。利用 XFdtd 的用户定义波形功能,工程师可以导入由各种测试标准定义的 ESD 波形,并用它们在 XFdtd 项目中创建 ESD 电流源。 此时,可以创建 ESD 仿真器/射枪模型,并用于在感兴趣的位置激发 DUT 的几何形状,然后对由此产生的电磁场和电流进行仿真和分析。

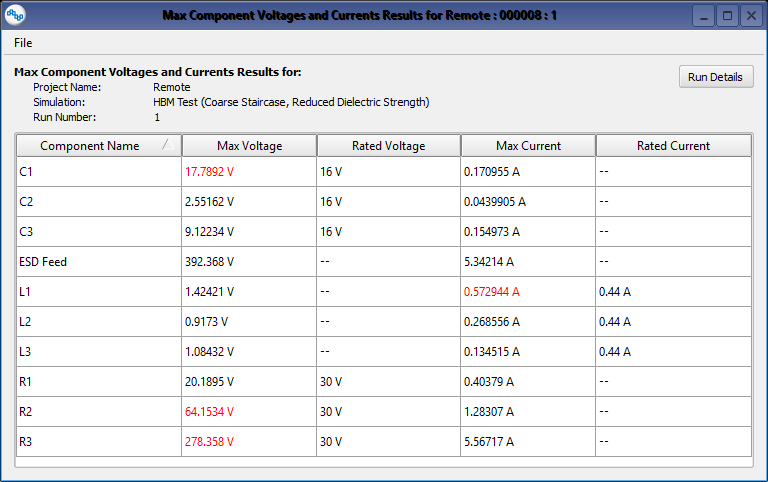

电路元件过电压和过电流

一般来说,在 ESD 测试中,电路元件故障比介质击穿故障更常见。 为预测电路元件故障,可将额定电压和电流输入参数添加到 XFdtd 的电路元件定义中,这些参数可从电子元件数据表中获取。 完成 XFdtd 仿真后,XFdtd 的 "最大元件电压和电流 "结果对话框会报告超出额定设计参数的元件。

优化 ESD 缓解措施

虽然模拟不能也不应该完全取代硬件测试,但它可以让 ESD 工程师深入了解 ESD 故障的可能发生位置,并在硬件原型阶段之前优化 ESD 缓解设计。 XFdtd 能够准确定位可能发生介电击穿的位置,并报告电路元件在 ESD 事件中超出设计参数的情况,从而降低产品开发成本,缩短产品上市时间,同时提高产品可靠性和消费者信心。

其他信息

-

网络研讨会

XFdtd 用于 TVS 二极管 ESD 保护的瞬态电磁/电路协同仿真

在本次网络研讨会上,您将了解 XFdtd 的瞬态电磁/电路协同仿真如何在设计流程的早期阶段有效解决 ESD 漏洞,并防止未来的认证受挫。

探索 资源

-

出版物

XFdtd® 的新功能

XFdtd 7.11.1 版引入了多项增强功能,旨在提高仿真精度、扩展分析功能并简化工程工作流程。该版本反映了 Remcom 对解决天线设计、PCB 建模和相控阵系统开发中的高价值挑战的持续关注。

探索 资源

出版物

XFdtd 中的瞬态电磁/电路协同仿真:近距离观察用于 ESD 保护的 TVS 二极管

本文介绍了 XFdtd 的瞬态电磁/电路协同仿真功能,它结合了三维全波电磁仿真的优势和电路求解器的灵活性。

探索 资源